# National Spherical Torus Experiment (NSTX)

# **Power Supply Real Time Controller**

C. Neumeyer, R. Hatcher, R. Marsala, S. Ramakrishnan

Princeton University Plasma Physics Laboratory\* Princeton, New Jersev 08540

# Abstract

The NSTX [1] is a new national facility for the study of plasma confinement, heating, and current drive in a low aspect ratio, spherical torus (ST) configuration. The ST configuration is an alternate magnetic confinement concept which is characterized by high  $\beta$  (ratio plasma pressure to magnetic field pressure) and low toroidal field compared to conventional tokamaks, and could provide a pathway to the realization of a practical fusion power source.

The NSTX depends on a real time, high speed, synchronous, and deterministic control system acting on a system of thyristor rectifier power supplies to 1) establish the initial magnetic field configuration; 2) initiate plasma within the vacuum vessel; 3) inductively drive plasma current; and 4) control plasma position and shape. For the initial "day 0" 1st plasma operations (Feb. 1999), the system was limited to closed loop proportional-integral current control of the power supplies based on preprogrammed reference waveforms. For the "day 1" phase of operations beginning Sept. 1999 the loop has been closed on plasma current and position. This paper focuses on the Power Supply Real Time Controller (PSRTC).

#### I. INTRODUCTION

During a pulse the typical sequence of events is as follows:

• Central Ohmic Heating (OH) solenoid coil is precharged

- TF is applied

- · Fuel gas is injected

• OH coil current is rapidly decreased; resultant toroidal loop voltage ionizes the fuel gas

- Plasma current is driven by induction via OH coil

- PF coils (1a, 1b, 2, 3, 4, and 5) are used to control plasma shape and position

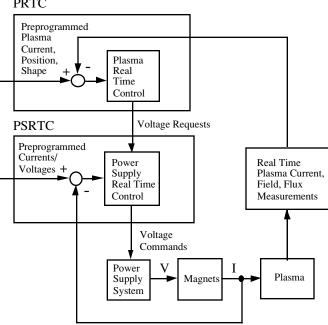

A conceptual block diagram of the system is given in Figure 1. Typically, upon initiation of a pulse the Power Supply Real Time Controller (PSRTC) performs closed loop current control to precharge the OH coil, initiate the TF coil current, and pre-bias other PF coils as required. Then, at the start of a pre-programmed time

PRTC

Figure 1-Block Diagram of Control System

window, the Plasma Real Time Controller (PRTC) initiates the plasma and controls plasma current, position, shape, etc. via voltage requests to the PSRTC. Upon termination of the plasma current the PSRTC extinguishes the current in all coil systems according to pre-programmed current derivatives.

# **II. POWER SUPPLIES & CIRCUITS TO BE CONTROLLED**

#### A. Power Supplies

NSTX utilizes the PPPL "Power Supply" (PS) facility originally built for the Tokamak Fusion Test Reactor (TFTR) project, consisting of thirty-nine (39) modular 12-pulse phase controlled thyristor rectifiers. Twenty-one (21) of the units are used for NSTX (total installed capacity for NSTX is 500MVA). Each PS consists of two 6-pulse "Power Supply Sections" (PSS) which are electrically isolated from each other but subject to the same "Firing Generator" (FG). Each PSS

<sup>\*</sup> Under USDOE Contract #DE-AC02-76-CHO3073

is equipped with a full rated bypass module which can carry the load current when the rectifiers are suppressed. Each PSS is rated to produce a maximum average DC output voltage of 1012.85VDC ( $\approx$ 1kV), no load, with 13.8kV AC input voltage applied to the converter transformer primary. Nominal pulse current rating of each PSS is 24kA-6sec/300sec. The FG of each PS controls, in effect, the voltage produced by its two PSS by phase controlling the thyristor firing pulses in accordance with a Control Word received as an input from the PSRTC. The Control Word is an 11 bit digital command.

#### B. Circuits

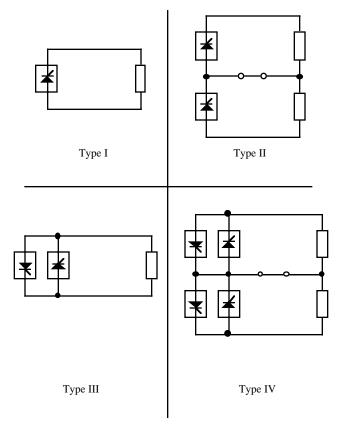

Circuit types to be controlled are as depicted in Figure 2, where the boxed thyristor symbol represents one or more PSS connected in series/parallel combination. The lines connecting the circles represent removable bus links.

Figure 2 - NSTX Circuit Configurations

a. Type I is a "Unipolar", "2-Wire" circuit. Current flows in one direction through one load coil group.

b. Type II is a "Unipolar", "3-Wire" circuit. Current flows in one direction through two load coil groups; the magnitude of the current may be different in the two "twin" load coil groups.

c. Type III is a "Bipolar", "2-Wire" circuit. Current flows in either direction through one load coil group.

d. Type IV is a "Bipolar", "3-Wire" circuit. Current flows in either direction through two load coil groups; the magnitude and polarity of the current may be different in the two "twin" load coil groups.

A listing of the NSTX circuits along with type, number of DC poles, and number of PSS is given in Table 1.

The voltage applied to, or the current produced in, each of the circuits must be explicitly controlled. Therefore, eleven (11) separate circuit control loops are required in case all of the bus links are in place, plus one spare, for a total of twelve (12). However, if the bus links are not installed in the Type II and Type IV circuits, then they reduce to Type I and Type III, respectively, and the number of explicit control loops is correspondingly reduced. When the bus links are not in place two halves of the former Type II or Type IV circuits are treated in all respects by the PSRTC as single Type I or Type III circuits, respectively.

| Circuit    | Туре   | DC Poles | Series/Paralle |

|------------|--------|----------|----------------|

|            |        |          | 1              |

|            |        |          | PSS            |

| TF         | Ι      | 2        | 1/4            |

| OH         | Ш      | 2        | 6/2            |

| PF1a Upper | Π      | 3        | 2/1            |

| PF1a Lower |        |          | 2/1            |

| PF1b       | Ι      | 2        | 2/1            |

| PF2 Upper  | II     | 3        | 2/1            |

| PF2 Lower  |        |          | 2/1            |

| PF3 Upper  | IV     | 3        | 2/1            |

| PF3 Lower  |        |          | 2/1            |

| PF4/5      | Ι      | 2        | 2/1            |

| CHI        | Ι      | 2        | 2/2            |

| Spare      |        | 2        | 2              |

| Total      | 12 ckt | 21 pole  | 42 PSS         |

|            |        |          |                |

Table 1 - NSTX Circuit Types, Poles, and PSS

# **III. POWER SUPPLY REAL TIME CONTROLLER**

### A. Power Supply Control Function

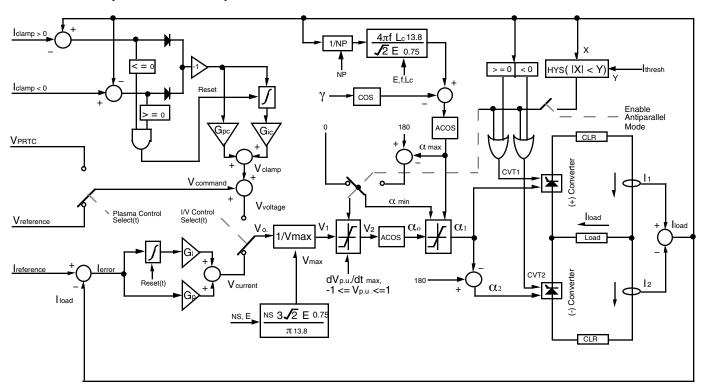

The Power Supply Control Function is depicted in Figure 4. The same basic function is applied to all of the circuits. The output of the control function consists of the firing angle ( $\alpha$ ) and convert bit commands which are delivered to the PS in the form of the PS Control Words. Since the firing angle is related to the voltage, these commands are, essentially, voltage commands. The voltage commands are derived either from closed loop proportional - integral (PI) current control against a programmable reference, or from a direct voltage

request. The direct voltage request is obtained from either a programmable reference, or a signal supplied in real time by the PRTC. When in the voltage control mode, a current clamp feature is applied if the current approaches a programmable limit. Additional features include rate limiting, and control of antiparallel rectifiers, including the required  $\alpha$  limiting. Following is a description of these features, with reference to Figure 4.

#### 1) Closed Loop Current Control

The load current  $I_{load}$  is subtracted from a programmable reference  $I_{reference}$ . The difference is the error  $I_{error}$ .  $I_{error}$  is multiplied by proportional gain  $G_p$ , and is integrated and multiplied by integral gain  $G_i$ . The sum of these two terms is the voltage requested by current control  $V_{current}$ . The integrator includes an "anti-wind-up" reset feature which is a function of time; one reset time is allowed per circuit.

#### 2) Voltage Control & Current Clamp

The source of the command  $V_{command}$  can be either the programmable reference  $V_{reference}$  or a real time signal provided by the PRTC (VPRTC). The time window during which VPRTC is set by preprogrammed plasma start and end times. Voltage control is subject to an override by a current clamping feature which comes into play when limits are reached. The clamping is based on PI control which generates a voltage adjustment term  $V_{clamp}$  whenever the load current I<sub>load</sub> passes outside the range between the positive and negative clamp settings I<sub>clamp>0</sub> and I<sub>clamp<0</sub>. When the current returns to the allowable range the clamp integrator is reset. The net voltage request based on voltage control V<sub>voltage</sub> is the result of the addition of V<sub>command</sub> and V<sub>clamp</sub>.

#### 3) Voltage to Alpha Conversion

The selection of the source of the voltage request  $V_0$ from either voltage control Vvoltage or current control V<sub>current</sub> is a function of time. V<sub>1</sub> is the per unit version of V<sub>0</sub> based on V<sub>1</sub>=V<sub>0</sub>/V<sub>max</sub>, where V<sub>max</sub> is the maximum no-load voltage available for the circuit in question. V<sub>max</sub> is based on the programmable number of series PSS (NS), and the primary side AC rms line-toline source voltage E (nominally 13.8kV at D-site). V2 is a rate and magnitude limited version of V1, where the rate limit is programmable for each circuit and the magnitude limit is -1 to 1 per unit. The rate limit is only applied when the antiparallel mode is in effect (see next section).  $\alpha_0$  is the firing angle request, and  $\alpha_1$  is the final firing angle command after limiting. If antiparallel operation is not in effect, then the allowable range of  $\alpha_1$ is 0 to  $\alpha_{max}$ , where  $\alpha_{max}$  is the maximum permissible delay angle. It is calculated based on the load current per PSS, equal to Iload/NP where NP is the number of parallel PSS branches in the circuit being controlled, the AC source frequency  $\omega$ , the commutating inductance L<sub>c</sub>, and the AC source voltage E, along with a programmable inversion margin angle  $\gamma$ . If antiparallel operation is in effect, then the minimum permissible delay angle  $\alpha_{min}$  is set equal to  $180 - \alpha_{max}$ , so that the allowable range of alpha is therefore  $\alpha_{min}$  $\leq \alpha_1 \leq \alpha_{max}$  in the antiparallel mode.

#### 4) Antiparallel Operation

Antiparallel Operation permits bipolar current flow in the load without delay around current zero. When it is in effect, the antiparallel converters (a.k.a. the (+) and (-) converters) must be operated at symmetric (about 90 degrees) delay angles  $\alpha_{min}$  and  $\alpha_{max}$ . This is required to minimize the circulating current which is impeded only by the Current Limiting Reactors (CLRs). The antiparallel mode is declared when the magnitude of the load current I<sub>load</sub> falls below a threshold I<sub>thresh</sub>. Thus the comparison is conditioned by a hysteresis function which only declares the mode to be true if the previous magnitude exceeded the threshold. A switch is provided to enable/disable antiparallel operation for each circuit.

# B. Current Measurements

PSS branch currents are measured by several types of DC current transducers. Redundant measurements are provided in each branch. At each time step, the difference between the magnitude of the two measurements is calculated (after applying scale factor including polarity) and compared to a programmable allowable as a check for the validity of the measurements. The measurement with the larger magnitude is used for further processing. The coil currents  $I_{load}$  are obtained from the sum of the individual branch measurements.

# C. Protection Features

Following protection features are provided in the PSRTC:

- instantaneous overcurrent protection

- single pulse  $\int i2(t)dt$  protection

- adiabatic coil temperature rise protection

• RMS current checks (based on continuous simulation of heating (during pulse) and cooling (between pulses) of DC cable systems.

# D. Simulation Mode

In order to test the PSRTC, a simulation package is attached which interfaces with the real time control code at the same points of input and output as in normal operation (the inputs being the PSS branch currents and the outputs being the  $\alpha$  commands to the power supplies. Following features are included:

• Transient solution of mutually coupled L/R circuits (10 simulation time steps per control system time step) using PPPL's LRSIM code

• Simulation of latency of input data by utilization of simulation results obtained midway between control system time steps as inputs to control algorithm

• Simulation of transient heating of coils and its effect on ohmic resistance

• Simulation of delays and limits of power supplies; however individual thyristor commutations are not modeled

#### E. Implementation

The PSRTC is written primarily in FORTRAN (some adjuncts are in C) and runs on a VME based computer system inherited from prior experiments at PPPL [2]. It consists of the following components:

• Themis host computer (Sparc 10 running Sun OS)

- ethernet connectivity

- user interface

- data management and software development

- Skybolt I Shamrock real time computer

- four parallel Intel 80860 processors

- 64MB shared memory

- DMA port

- Precision Filters data acquisition system (DAS)

- two 32 channel analog input modules

- 10kHz

- DMA to Skybolt

#### • Power Conversion (PC) Link driver

interface to serial command link which distributes commands to 39 distributed PS at PPPL facility

The PSRTC occupies one of the four parallel i860 processors; the other three are available to the PRTC. The control system update rate is 1kHz (once per millisecond). Typical execution time of the PSRTC algorithms with all circuits running is less than 800µS.

The PSRTC utilizes 47 of the 64 DAS channels available. The remainder are reserved for the PRTC Ip, flux loop, and B probe signal inputs. These signals are transmitted from the transducers located in the NSTX test cell to the location of the control computer rack via analog fiber optic links.

Figure 4- Power Supply Control Function

# F. Future Plans

An upgrade to a new computer system is planned for summer 2000 (a.k.a. "day 2"). This will include:

- Upgraded host computer

- Upgraded Sky computer

• Distributed data acquisition system based on multiple VME crates strung together using fiber optic links and Front Panel Data Port (FPDP) direct access to the real time processor. The new computer system is not required in principle for the PSRTC but will instead facilitate an advance in the PRTC development, including more than a doubling of the number of inputs.

# REFERENCES

[1] C. Neumeyer et. al., "NSTX Constuction, Commissioning, and Initial Operations", 18<sup>th</sup> SOFE

[2] S. Ramakrishnan et al, "NSTX Electric Power Systems",  $18^{th}$  SOFE